# FRANK FERRANTE

October 2019

#### **Legal Notices**

This presentation contains information provided by Intel Corporation ("Intel"), and may refer to Intel's plans and expectations for the future, which are provided for discussion purposes only and are subject to change without notice. Forward-looking statements involve a number of risks and uncertainties: Refer to Intel's SEC filings for authoritative discussion of Intel's results and plans. This presentation imposes no obligation upon Intel to make any purchase, and Intel accepts no duty to update this presentation based on more current information. Intel is not liable for any damages, direct or indirect, consequential or otherwise, that may arise, directly or indirectly, from the use or misuse of the information in this presentation. Copyright © 2019 Intel Corporation. Intel and the Intel logo, are trademarks of Intel Corporation in the U.S. and/or other countries. Other names and brands may be claimed as the property of others.

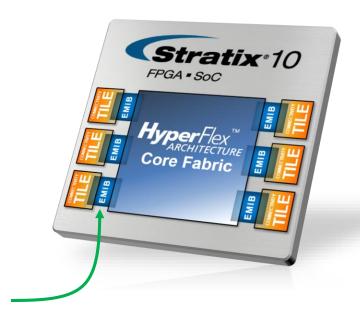

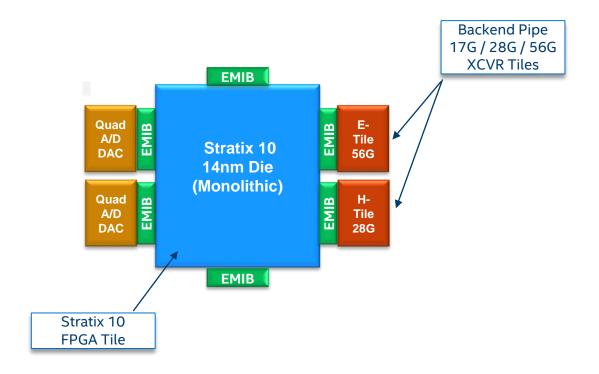

#### Heterogeneous 3D System-in-Package (SiP) Integration

Efficient and scalable integration using Intel's Embedded Multi-Die Interconnect Bridge (EMIB)

New class of FPGAs and MCPs to enable higher efficiency and flexibility

Enables convergence of process nodes and system functions into a single device

Mix and match process nodes

Enables higher efficiency and flexibility

Up to 1 Tbps full duplex on each EMIB Interface

Reduces size, weight and power

### Heterogeneous 3D System-in-Package (SiP) Integration

Efficient and scalable integration using Intel's Embedded Multi-Die Interconnect Bridge (EMIB)

New class of FPGAs to enable higher efficiency and flexibility

Enables convergence of process nodes and system functions into a single device

Mix and match process nodes

Enables higher efficiency and flexibility

Up to 1 Tbps full duplex on each EMIB Interface

Reduces size, weight and power

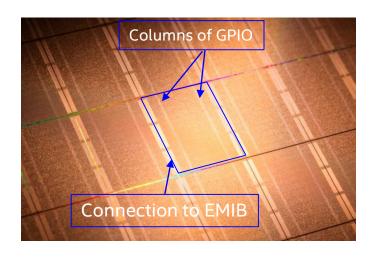

#### EMIB - Intel's Embedded Multi-Die Interconnect Bridge

• µ-bump C4 bump **Bump Images** Stratix 10 Packaging with EMIB Technology **Package Lid FPGA Die** 3D Tile 80000 Stratix 10 8 0000000000000000000000 **Package Substrate** with EMIB **Circuit Board**

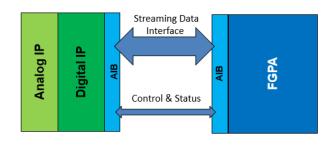

#### **AIB Overview**

Supports peer-to-peer high bandwidth parallel communication

Versatile per-channel clocking in both directions

Streaming or transactional protocols can be implemented on top of AIB

AIB's flexible IO cell permits arbitrary TX, RX, clock and control mapped by the protocol layer above

| AIB Power Advantages    |               |               |  |

|-------------------------|---------------|---------------|--|

| Metric                  | SERDES        | AIB           |  |

| Energy                  | 17pJ/bit [12] | 1 pJ/bit [11] |  |

| Power (500Gbps example) | 8.5W          | 0.5W          |  |

|                        | JESD204C | AIB  |      |

|------------------------|----------|------|------|

| Maximum line rate      | 32       | 2    | Gbps |

| Total Digital Delay TX | 17.53    | 0.75 | ns   |

| Analog Delay TX        | 2        | 1    | ns   |

| PCB/interposer Delay   | 0.31     | 0.06 | ns   |

| Analog Delay RX        | 2        | 1    | ns   |

| Total Digital Delay RX | 20.62    | 0.75 | ns   |

| Total Delay            | 42.46    | 3.56 | ns   |

**AIB Latency Comparisons**

The performance figures shown are optimized on Intel technology. Performance varies based upon system configuration.

## **Integrated Mixed Signal 2**

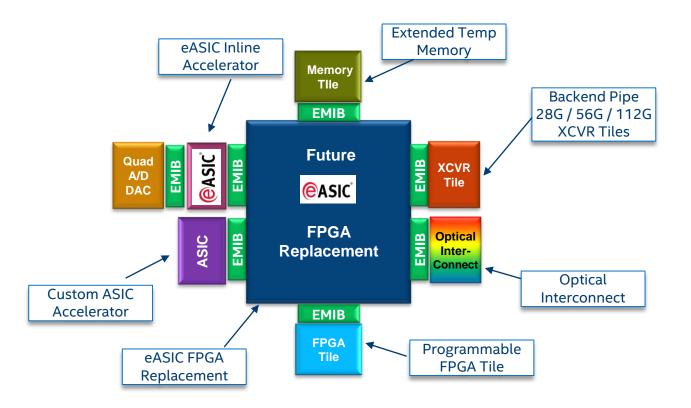

#### Future System Concept: + Customer ASIC

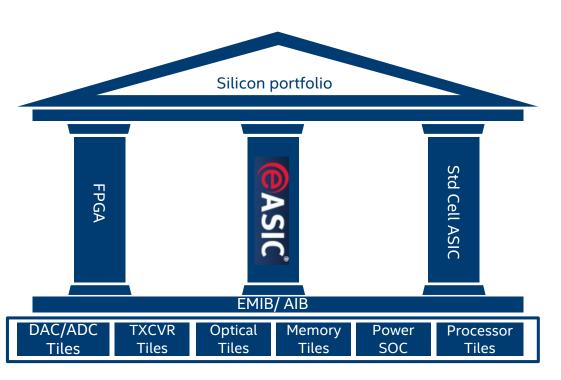

## Scalable Platform Strategy

## Enable silicon programmability and hardened customization

- ✓ Optimized by market

- √ Further optimized by customer

- √ Tailored capability to desired combination of TTM, cost, power, integration

#### Reduce customer's R&D spend

- √ Consistent IP across pillars

- √ Software and package compatibility

- √ Maximizes reuse

#### Mix and match pillars and tiles

- Leverage chiplet strategy to integrate independent of node

- ✓ Blend pillar components for optimal power, performance, cost